Coreboot is an alternative and open source firmware. Together with its payloads it can replace a BIOS or UEFI.

I was not able to find binary packages of coreboot. Maybe that is, because it is so hardware specific and would somehow make its usefulness questionable. However the latest source code version is here.

Why?

- Take back control: Own a hardware device and its software!

- Brand your device so that even removing the hard disk does not help.

- Write your own low level code. You know what? User space programs have no direct access to the contents of the flash.

- Your life bores you and you want to risk something - clearly speaking: This procedure can very well brick your device!

Hardware requirements #

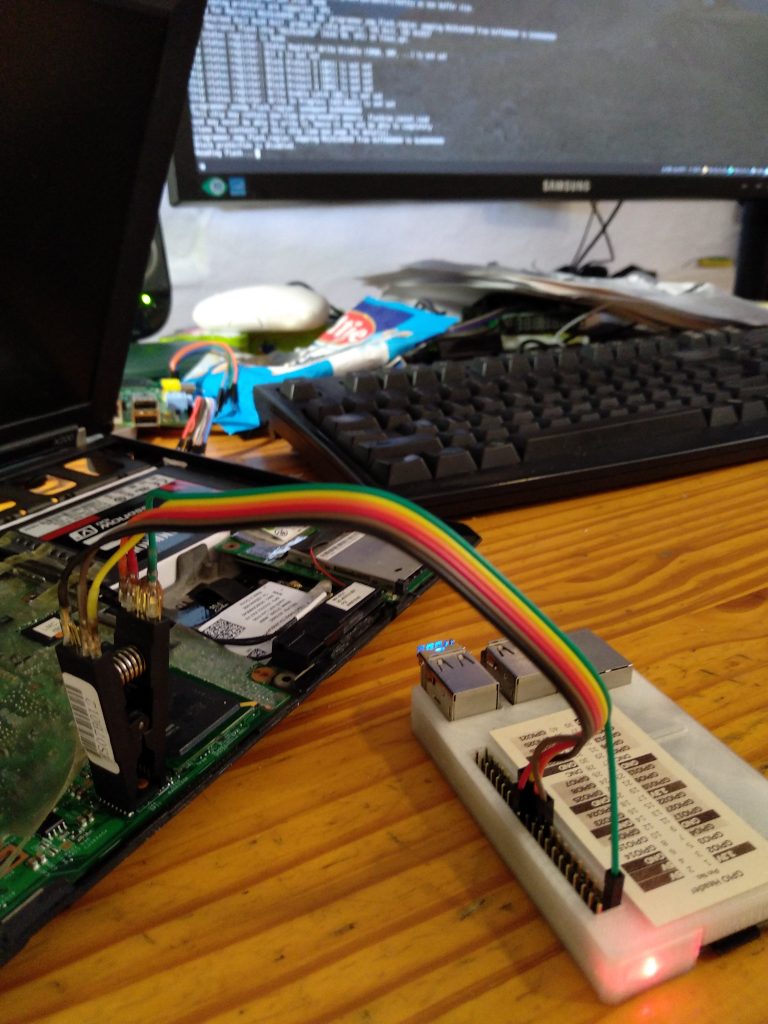

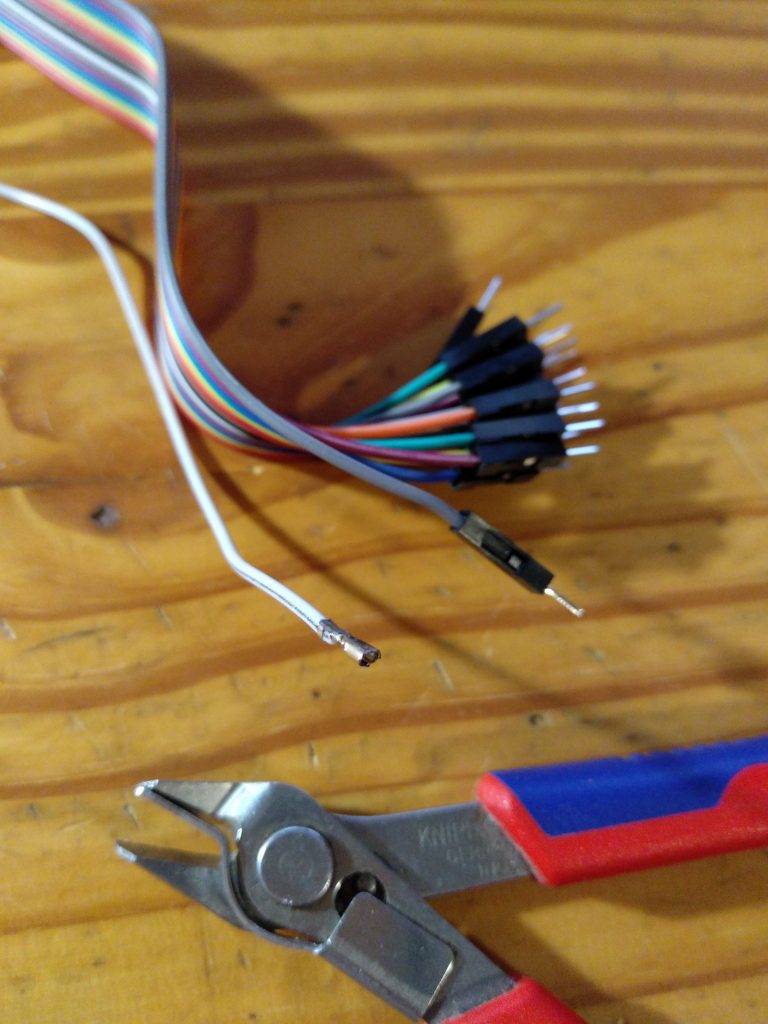

You better have one of these chip clips, best searched with soic16 clip. The

cheapest I could find has a small pin pitch (see pictures). I once soldered a

soic8 clip, but this time I used modified header cables and flexible heat

shrink and only press fitted these. I found that very convenient and it worked

perfectly, see here:

How to compile

- Download the source code

- run

make helpfor a first orientation - run

make nconfig\- if you want a splash image, also set

Devices -> Display -> Framebuffer mode: Linear "high-resolution" framebuffer

- if you want a splash image, also set

- run

make crossgcc ARCH=x64 CPUS=8 - run

make ARCH=x64 CPUS=8 - where

ARCHis the target architecture andCPUSthe number of cores to use for compilation- The default of one takes really long. - copy the image

coreboot.romto the system from which you can do the in system programming (e.g. the raspberry, but you may have a USB SPI device)

How to flash #

Check the cable connection by reading the chip identifier:

flashrom -VVV -p linux_spi:dev=/dev/spidev0.0,spispeed=256 -c "MX25L6405D"

After that works read the contents out to a file:

flashrom -VVV -p linux_spi:dev=/dev/spidev0.0,spispeed=256 -c "MX25L6405D" -r read_01.rom

Repeat the last step three times and compare the files, e.g. with

md5sum *

If there are read errors reduce the spispeed, e.g. half it. If all went

good, read the memory layout out:

ifdtool -f rom.layout read_01.rom

The last step is not strictly necessary, but it helps if you messed

something up, e.g. if you flashed the chip before, it was automatically

erased to some extend and the ifd switch from flashrom does not work

any more.

Next step would be to write the new BIOS (and BIOS only):

flashrom -f -p linux_spi:dev=/dev/spidev0.0,spispeed=128 -c "MX25L6405D" -w coreboot.rom -l rom.layout image bios noverify-all

If you see errors like "trying next erase method", further reduce the

spispeed!

Otherwise you should be done! Hurray!